搜索结果: 1-15 共查到“工学 微电子”相关记录1937条 . 查询时间(0.34 秒)

成都工业学院电子工程学院微电子科学与工程专业介绍

微电子 成都 工业学院

<

2024/4/8

成都工业学院电子工程学院微电子科学与工程专业前身是2003年在国内首批设立的微电子技术专业,2012年获批四川省首批卓越工程师教育培养计划专业,2017年入选四川省首批地方普通本科院校应用型示范专业,2019年入选国家“双万计划”省级一流专业,2020年入选国家“双万计划”国家级一流本科专业。与英特尔产品(成都)有限公司、杭州士兰集成电路有限公司等知名企业开展校企合作,培养以集成电路制造工艺技术和...

中国科学院微电子所等在数模混合存算一体芯片方面获进展(图)

芯片 人工智能 元件

<

2024/2/29

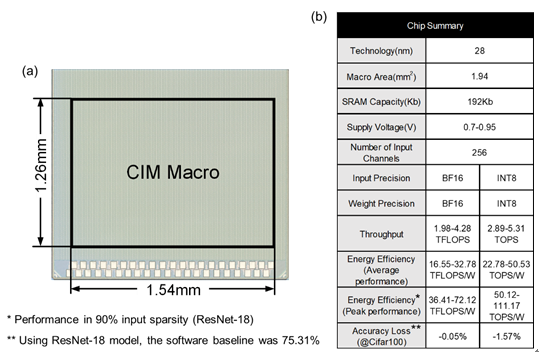

当前,基于边缘智能计算设备运行的人工智能应用日趋复杂和高精度。为降低边缘设备运行的延迟和功耗,存算一体技术被应用在边缘设备端,通过减小数据搬运的开销最大化减少边缘设备上的延迟与功耗。而传统的存算一体宏仅支持使用整数型数据计算,难以支持日趋高精度、高复杂度以及片上训练的边缘端智能计算任务。仅使用单一模拟或数字方案的存算一体宏,难以在能量效率、面积效率和精度上取得最优化。如何有效结合模拟存算与数字存算...

中国科学院微电子所在数模混合存算一体芯片方面取得重要进展(图)

芯片 智能计算

<

2024/2/28

当前,基于边缘智能计算设备运行的人工智能应用日趋复杂及高精度,为降低边缘设备运行的延迟和功耗,存算一体技术被应用在边缘设备端,通过减小数据搬运的开销最大化减少边缘设备上的延迟与功耗。但传统的存算一体宏仅支持使用整数型数据计算,难以支持日趋高精度、高复杂度以及片上训练的边缘端智能计算任务。且仅使用单一模拟或数字方案的存算一体宏,在能量效率、面积效率和精度上难以取得最优化。如何有效结合模拟存算与数字存...

中国科学院微电子所在片上学习存算一体芯片方面取得重要进展(图)

一体芯片 神经网络 智能计算

<

2024/2/28

当前,智能计算设备呈指数式增长,迫切需要低功耗与低延迟执行神经网络推理任务,以及不依赖云端的片上学习能力来动态适应边缘端复杂多变的应用场景。非易失存算一体技术可最大化减少数据搬运带来的功耗和延迟并消除静态功耗,为边缘智能计算设备提供了一种极具竞争力的方案。非易失存算一体芯片近年来持续快速发展,其在集成规模、能效、算力等方面均取得了长足的进步,实现了对片上推理任务的高效支持。但进行片上学习通常需要对...

杭州电子科技大学微电子研究院科研成果获奖(2013年-2022年)

杭州电科大 微电子研院 科研成果 获奖

<

2024/2/4

杭州电子科技大学微电子研究院科研成果项目(2018-2023年)

杭州电子科技大学微电子研究院

<

2024/2/4

杭州电子科技大学微电子研究院科研成果专利(2020年-2023年)

杭州电科大 微电子研院 科研成果 专利

<

2024/2/4

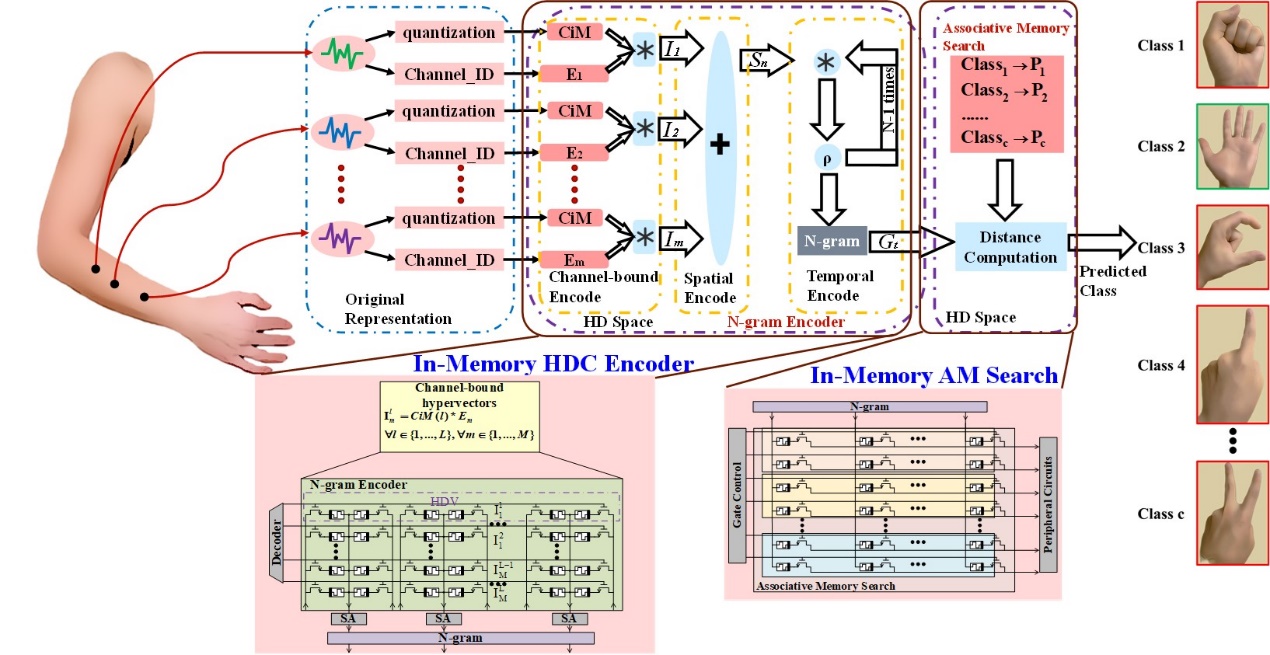

中国科学院微电子所在存内高维计算时空信号编码方面取得进展(图)

高维计算 时空信号 编码 传感器

<

2024/2/28

时空信号是指在特定时间窗口内(时间域)并包含有多个通道(空间域)的数据信息,如生物信号、气候信号、视频信号以及多模态的各种传感器信号等等。随着大数据、人工智能以及物联网技术的发展,越来越多的边缘智能设备得到普及。如何在边缘设备上实时处理、分析和解释时空信号已成为未来社会智能化发展的一项重要挑战。

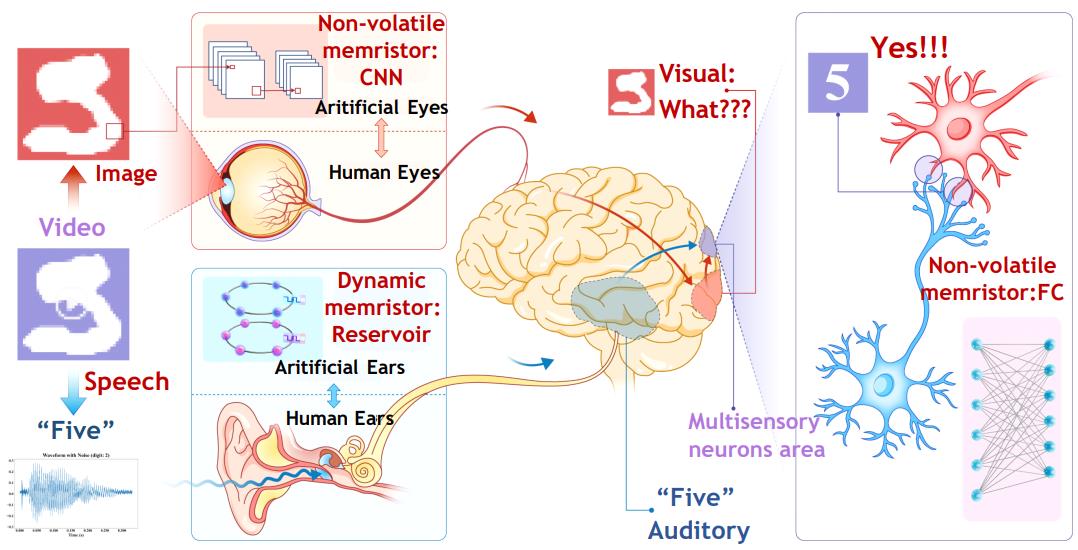

中国科学院微电子所在多模态三维神经形态计算领域取得重要进展(图)

三维神经 形态计算 微电子

<

2024/2/28

微电子所重点实验室刘明院士团队设计了一种新的3D垂直RRAM阵列,其中不同层器件分别具有非易失性和易失性,这使得它能够构建多模态神经形态计算网络。第1层器件(字线:TiN)和第2层器件(字线:Ru)分别表现出不同的动态特性,可以用于构建多时间尺度储备池计算网络;第3层器(WL:W)表现出了多比特存储的非易失特性,可用于构建卷积神经网络和全连接网络等。第1层和第2层器件构建的多时间尺度储备池计算网络...

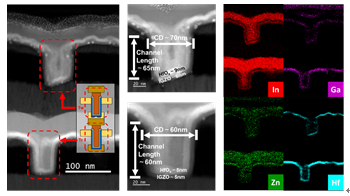

中国科学院微电子所在CAA结构的3D DRAM研究领域取得重要进展(图)

结构 器件 晶体管

<

2024/2/28

DRAM是存储器领域最重要的分支之一。随着尺寸微缩,1T1C结构DRAM的存储电容限制问题愈发显著,导致传统1T1C-DRAM面临微缩挑战。基于铟镓锌氧(IGZO)晶体管的2T0C-DRAM有望克服1T1C-DRAM的微缩挑战,在3D DRAM方面发挥更大的优势。但现阶段研究工作都基于平面结构的IGZO器件,形成的2T0C单元尺寸(大约20F2)比相同特征尺寸下的1T1C单元尺寸(6F2)大很多,...

中国科学院微电子所在三维铁电存储器噪声特性应用方面取得进展(图)

芯片 集成 微电子

<

2024/2/29

传统贝叶斯机面临三大挑战:一是需要高质量的随机源生成具有真随机性的随机比特数流;二是由于随机变量随着问题的规模和复杂度的增加而增加,因此需要高密度的存储器;三是存储器和随机源的分离,导致了芯片面积和功耗的浪费。

中国科学院微电子所在阻变存储器芯片创新应用研究取得进展(图)

芯片 集成 细胞

<

2024/2/29

阻变存储器(RRAM)因其高速、低功耗和可扩展性而被广泛用于实现边缘计算加速器。但由于RRAM存在保持特性退化的问题,导致基于RRAM芯片上的网络推理准确率随时间的增大而降低,从而限制了基于RRAM的边缘计算加速器的运算精度。

中国科学院微电子所在面向存内计算的多比特2T0C DRAM研究中取得重要进展(图)

计算系统 薄膜材料 器件结构

<

2024/2/29

为解决现代计算系统中(如云计算和人工智能)的“内存墙”带宽局限、高效计算瓶颈和制造工艺尺寸微缩等问题,一种结合新型非晶态氧化铟镓锌(IGZO)薄膜材料的无电容(2T0C)DRAM结构,有望取代传统1T1C DRAM成为关键性的新兴技术路线。目前,大量研究工作集中于通过器件结构和工艺优化来提升IGZO 3D DRAM的保留时间和操作速度,但现有IGZO TFTs器件普遍存在性能均一性及阈值调控难题,...